Интегрированные сети ISDN

Формат IP PDU при транспортировке с использованием AALATM

Рисунок 4.3.5.20. Формат IP PDU при транспортировке с использованием AAL5 ATM

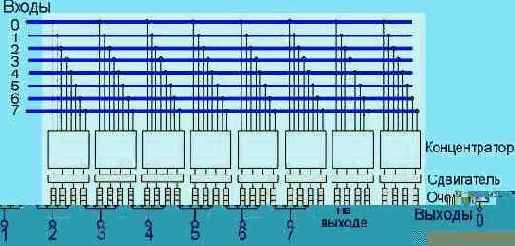

Пропускная способность сети АТМ (150 Мбит/с) позволяет передавать немного более 360000 ячеек в секунду, что означает для ATM-переключателя время коммутации менее 2,7 мксек. Реальный переключатель может иметь от 16 до 1024 входных линий, что может означать коммутацию 16-1024 ячеек каждые 2,7 мксек. При быстродействии 622 Мбит/с новая порция ячеек поступает каждые 700 нсек. Постоянство длины ячеек упрощает конструкцию ключа. Все АТМ-ключи имеют целью обеспечить коммутацию с минимальной вероятностью потери и исключить возможность изменения порядка следования ячеек. Приемлемой считается вероятность потери ячейки не более 10-12. Это эквивалентно для большого коммутатора потери 1-2 ячеек в час. Уменьшению вероятности потери способствует создание буферов конвейерного типа. Если на вход переключателя приходят две ячейки одновременно, одна из них обслуживается, а вторая ставится в очередь (запоминается в буфере). Выбор ячеек может производиться псевдослучайно или циклически. При этом не должно возникать предпочтений для каких-то каналов. Если в один цикл на вход (каналы 1, 2, 3 и 4) коммутатора пришли четыре ячейки, предназначенные для выходных линий J+2, J, J+2 и J+1, соответственно, то на линии J+2 возникает конфликт. Предположим, что будет обслужена ячейка, поступившая по первой входной линии, а ячейка на входной линии 3 будет поставлена в очередь. В начале следующего цикла на выход попадут три ячейки. Предположим также, что в этот цикл на ходы коммутатора (1 и 3) придут ячейки адресованные для линий J+3 и J, соответственно. Ячейка, адресованная J, будет поставлена в очередь вслед за ячейкой, адресованной J+2. Все эти ячейки будут переданы только на 4-ом цикле. Таким образом, попадание в очередь на входе ячейки блокирует передачу последующих ячеек даже если выходные каналы для их передачи свободны. Чтобы исключить блокировку такого рода можно организовать очередь не на входе, а на выходе коммутатора. При этом для коммутатора с 1024 входами теоретически может понадобиться 1024 буфера на каждом выходе. Реально число таких буферов значительно меньше. Такая схема АТМ-коммутатора (8*8) показана на Рисунок 4.3.5.21.